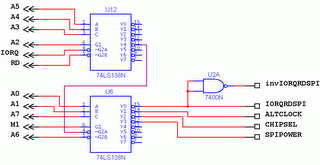

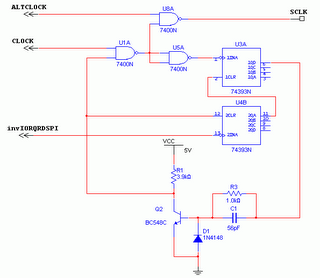

Este bloco possui também uma entrada para "Resetar" o contador, ativada pelo sinal de acesso ao endereço base. Desta forma, a cada execução da instrução "IN" do Z80, o contador é zerado e um novo ciclo de transferência é realizado.

clique na imagem para ampliar

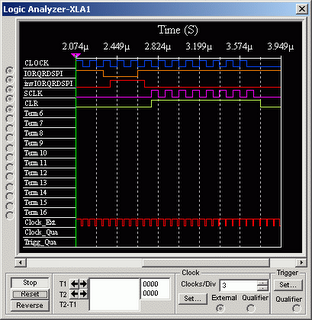

Embora simples, o gerador de Clock é a alma deste projeto, pois possibilita o ativamenteo dos registradores de deslocamento, e a transferência automática dos bits na velocidade do clock do Z80, eliminando a necessidade de se gerar por software os pulsos de clock e os deslocamentos (SHIFT) dos bits do byte a ser transmitido.

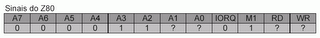

O Circuito final pode ser visto na figura abaixo:

clique na imagem para ampliar

O gerador de clock possui ainda uma entrada para Clock externo, comandada diretamente por um acesso a uma porta do Z80. Esta entrada foi acrescentada para poder gerar um sinal de, no máximo, 400KHz, necessário para a partida do cartão MMC/SD.

A fim de se economizar componentes, não tanto pelo preço sem si, mas pelo espaço ocupado pela placa, o inversor foi imlementado utilizando-se um transistor. O capacitor de 50pf em paralelo com o resistor de base, e o relativamente pequeno valor do resistor de coletor servem para acelerar as transições, que na simulação foram de aproximadamente uns 5ns.

Pelo mesmo motivo, o contador "ocioso" do 74LS393 foi transformado num flip-flop improvisado, de forma a resetar o contador quando o sinal de decodificação for desativado, ou seja, após o término da instrução "IN".

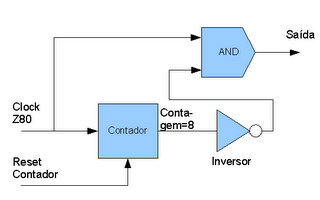

A forma de onda do sinal simulado para um clock de 8MHz pode ser vista na figura abaixo.

clique na imagem para ampliar